[ad_1]

A few weeks ago, we saw Apple announce its latest iPhone 13 series devices, a set of phones powered by the latest Apple A15 SoC. Today, ahead of the full device review we’ll be covering in the near future, we’re taking a closer look at the next-gen chipset, taking a look at exactly what Apple has changed in the new silicon, and if it lives up to the hype.

The A15’s announcement this year was a bit weirder on Apple’s PR side, not least because the company generally avoided making generational comparisons between the new design and Apple’s own A14. Particularly notable was the fact that Apple preferred to describe the SoC in the context of competition; while it’s not unusual on the Mac side, it’s something that stood out this year more than usual for the iPhone announcement.

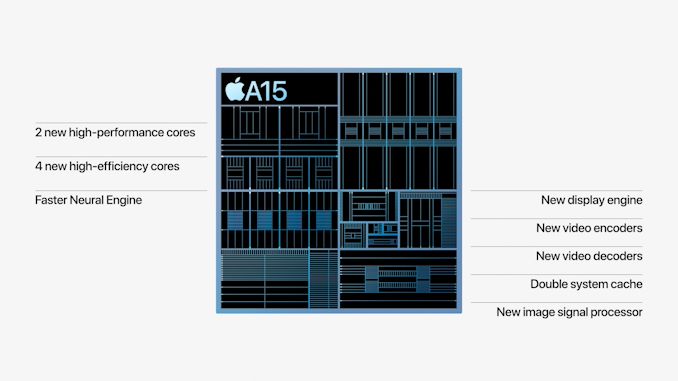

The few hard facts about the A15 were that Apple was using new designs for its processors, a faster neural engine, a new 4-core or 5-core GPU depending on the iPhone variant, and a whole new pipeline of display and multimedia hardware block for video encoding and decoding, as well as new ISP enhancements for camera quality advancements.

On the processor side, the improvements were very vague as Apple said it was 50% faster than the competition, and GPU performance metrics were also made this way, describing the A15 GPU as 4. cores being + 30% faster than the competition, and the 5-core variant being 50% faster. We’ve put the SoC to the test, and in today’s article we’ll focus on the exact performance and efficiency metrics of the new chip.

Frequency accelerations; 3.24 GHz performance and 2.0 GHz efficiency cores

Starting with the CPU side, the new A15 would feature two new CPU microarchitectures, both for performance cores and efficiency cores. The first reports on the performance of the new cores focused on frequencies, which we can now confirm in our measurements:

| Maximum frequency in relation to loaded threads Maximum MHz per core |

||||||

| Apple A15 | 1 | 2 | 3 | 4 | ||

| Performance 1 | 3240 | 3180 | ||||

| Performances 2 | 3180 | |||||

| Efficiency 1 | 2016 | 2016 | 2016 | 2016 | ||

| Efficiency 2 | 2016 | 2016 | 2016 | |||

| Efficiency 3 | 2016 | 2016 | ||||

| Efficiency 4 | 2016 | |||||

| Maximum frequency in relation to loaded threads Maximum MHz per core |

||||||

| Apple A14 | 1 | 2 | 3 | 4 | ||

| Performance 1 | 2998 | 2890 | ||||

| Performances 2 | 2890 | |||||

| Efficiency 1 | 1823 | 1823 | 1823 | 1823 | ||

| Efficiency 2 | 1823 | 1823 | 1823 | |||

| Efficiency 3 | 1823 | 1823 | ||||

| Efficiency 4 | 1823 | |||||

Compared to the A14, the new A15 increases the peak single-core frequency of the dual-performance central cluster by 8%, now reaching up to 3240 MHz compared to the 2998 MHz of the previous generation. When both performance cores are active, their operating frequency actually increases by 10%, with both now running at an aggressive 3180 MHz compared to the 2890 MHz of the previous generation.

In general, Apple’s frequency increases here are quite aggressive given that it’s quite difficult to push this performance aspect of a design, especially when we don’t expect major performance gains from the customer. new process node. The A15 is expected to be made on an N5P node variant from TSMC, although neither company is really divulging the exact details of the design. TSMC claims a + 5% increase in frequency over N5, so for Apple to go further this would have indicated an increase in power consumption, something to keep in mind as we delve deeper into the features of processor power.

The electronic cores of the A15 are now capable of clocking up to 2016 MHz, a 10.5% increase over the cores of the A14. The frequency here is independent of the performance cores, because the number of threads in the cluster does not affect the other cluster, or vice versa. Apple has made some more interesting changes to the little hearts of this generation, which we’ll get to in a moment.

Giant caches: 12MB L2 performance CPU, massive 32MB SLC

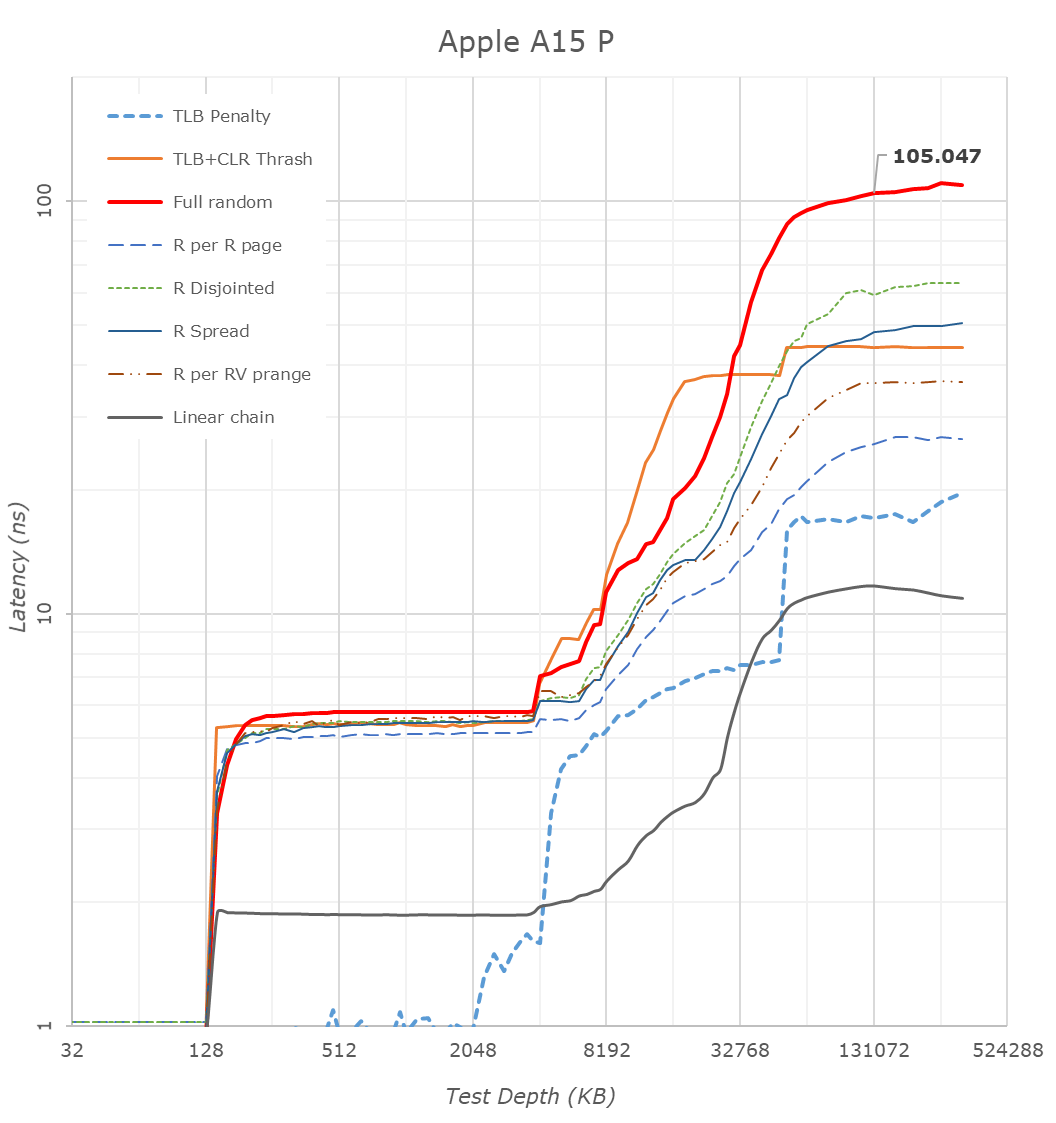

Another simple technical detail that Apple revealed when it launched was that the A15 now has double the system cache compared to the A14. Two years ago, we detailed the new SLC for the A13, which had gone from 8MB in the A12 to 16MB, a size that was also kept constant in the A14 generation. Apple claiming they’ve doubled that would therefore mean it’s 32MB now in the A15.

Looking at our latency tests on the new A15, we can indeed now confirm that the SLC has now doubled up to 32MB, pushing memory depth even further to hit DRAM. Apple’s SLC is likely to be a key factor in the chip’s energy efficiency, being able to keep memory accesses on the same silicon rather than using slower, less power-hungry DRAM. We’ve seen these types of last-level caches being used by more SoC vendors, but at 32MB the new A15 dwarfs competing implementations like the 3MB SLC on the Snapdragon 888 or the estimated SLC from 6-8MB on the Exynos 2100.

What Apple also did not disclose were changes to the performance core L2 cache, which has now grown by 50% from 8MB to 12MB. It was actually the same size. L2 than on the Apple M1, but this time around it only serves two performance cores instead of four. Access latency appears to have decreased from 16 cycles on the A14 to 18 cycles on the A15. On performance cores I am also seeing changes in L1 speeds as it seems to be able to do 1 cycle accesses to cache lines, as long as they are in the same page, same type of access on the A14 takes 3 cycles.

A 12MB L2 is once again huge, more than double the combined L3 + L2 (4 + 1 + 3×0.5 = 6.5MB) of other models such as the Snapdragon 888. It looks like Apple invested a lot of SRAM in this Generation of SoC of the Year.

Efficiency Cores this year don’t appear to have changed their cache size, remaining at 64KB L1D and 4MB shared L2, but we see that Apple has increased the L2 TLB to 2,048 entries, now covering up to 32 MB, likely to facilitate better SLC latency access. Interestingly, this year Apple is now allowing efficiency cores to have faster DRAM access, with latencies of around 130ns vs. + 215ns on the A14, again something to keep in mind. mind in the next section on article performance.

Changes in processor microarchitecture: one year (slower)?

This year’s CPU microarchitectures were a bit of a wildcard. Earlier this year, Arm announced the new Armv9 ISA, primarily defined by the new SVE2 SIMD instruction set, as well as the company’s new Cortex-series IP CPU that uses the new architecture. In 2013, Apple was known to be the first to hit the market with an Armv8 processor, the first 64-bit compatible mobile design. Against this background, I generally expected this year’s generation to feature v9 as well, but that doesn’t seem to be the case with the A15.

Micro-architecturally, the A15’s new performance cores don’t look much different from last year’s designs. I haven’t invested the time to examine every nook and cranny of the design yet, but at least the CPU backend is the same in terms of throughput and latency compared to the A14 performance cores.

Efficiency cores have undergone more changes, along with some changes to the memory subsystem TLB, the new electronic core now gains an additional full ALU bringing the total to 4, down from 3 previously. The heart could no longer be called “small” by any means, and it seems to have grown again this year, again, something we will be presenting in the performance section.

The possible reason for Apple’s more moderate micro-architectural changes this year could be a storm of a few factors – Apple notably lost its lead architect on the big performance cores, as well as parts of the design teams, to Nuvia. in 2019 (later acquired by Qualcomm earlier this year). Switching to Armv9 could also involve additional design work, and the pandemic situation could have contributed to a non-ideal execution as well. We’ll have to look at next year’s A16 to really see if Apple’s design pace has slowed down, or if it was just a slippage, or just a lull before a much bigger change. in the next microarchitecture.

Of course, the tone here describes a rather conservative improvement to the A15’s processors, which in terms of performance and efficiency are anything but that.

[ad_2]

Source link