[ad_1]

AnandTech Live Blog: The latest updates are at the top. This page will update automatically, there is no need to manually refresh your browser.

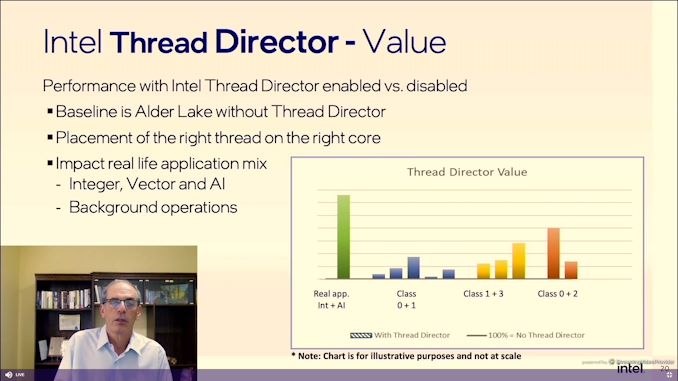

12:18 p.m. EDT – Help with asymmetry between the wires

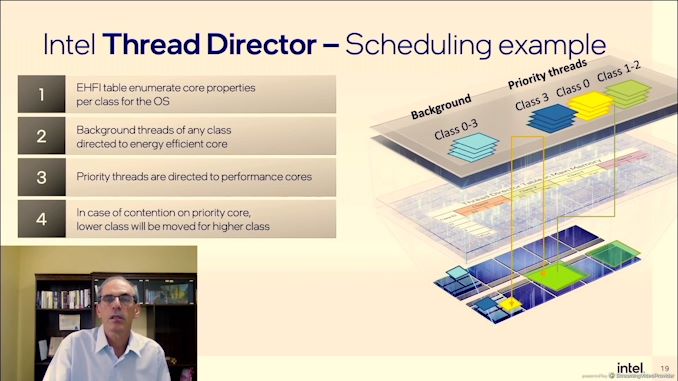

12:17 p.m. EDT – Here is an example of planning

12:15 p.m. EDT – The table is topology agnostic

12:15 p.m. EDT – The operating system planner is the final arbiter

12:14 p.m. EDT – The operating system has an idea of the priority of the thread

12:14 p.m. EDT – Thread Director Table updated less often than the thread classification

12:14 p.m. EDT – Sometimes it makes sense to merge a software thread with fewer cores, or one type of core

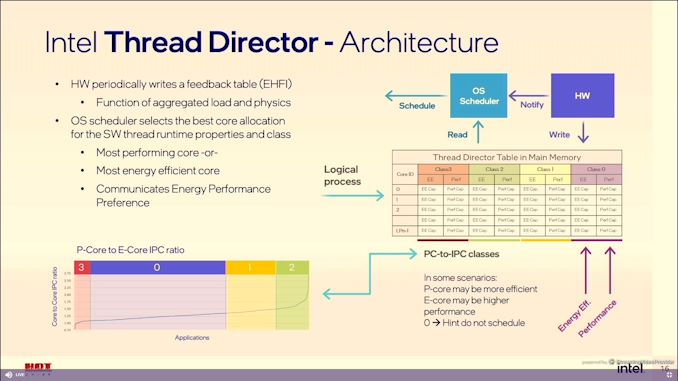

12:12 p.m. EDT – So each processor gets a section in the table, and it has a value for performance and efficiency, and the workload is compared

12:12 p.m. EDT – This is more details on Thread Director

12:11 p.m. EDT -Intel EHFI

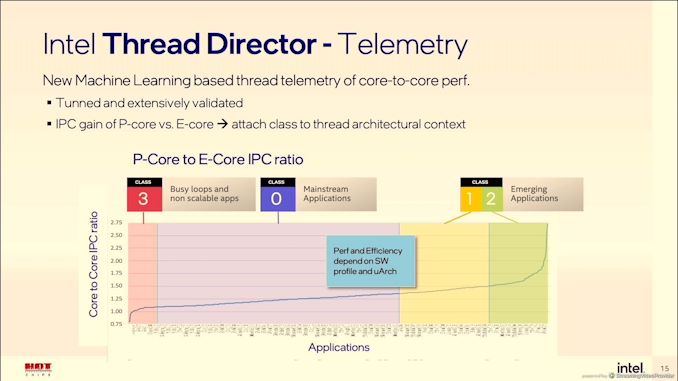

12:10 p.m. EDT – Core-to-Core IPC is the main metric

12:10 p.m. EDT – Thread Director will predict the workload class and divide it into classes for the OS scheduler on the order of 30 microseconds

12:09 p.m. EDT – Embedded microcontroller

12:08 p.m. EDT – Thread Director is mainly for Windows 11

12:08 p.m. EDT – Intelligence is built into the hardware

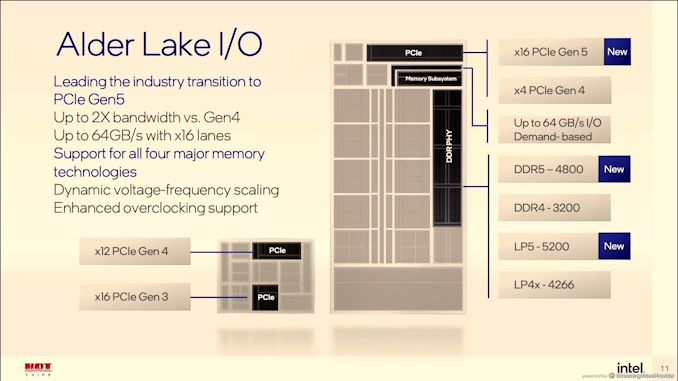

12:07 p.m. EDT – Only mobile will get native Thunderbolt

12:06 p.m. EDT – 96 UE on mobile, 32 UE on computer

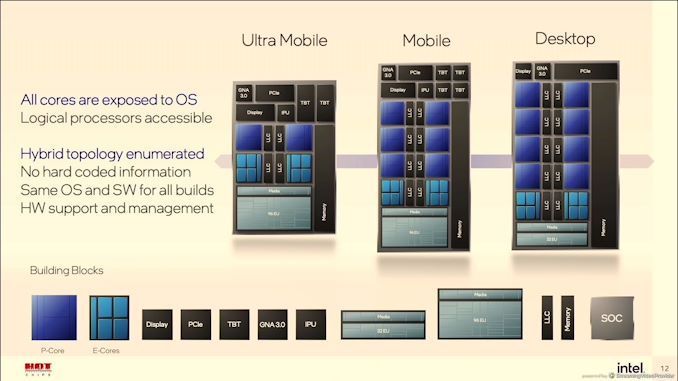

12:06 p.m. EDT – mix and match for future products

12:06 p.m. EDT – modular design

12:05 p.m. EDT – 2 + 8, 6 + 8 and 8 + 8 for P-core + E-core

12:05 p.m. EDT – UP3 / UP4 for mobile, desktop

12:05 p.m. EDT – Scalable SoC architecture

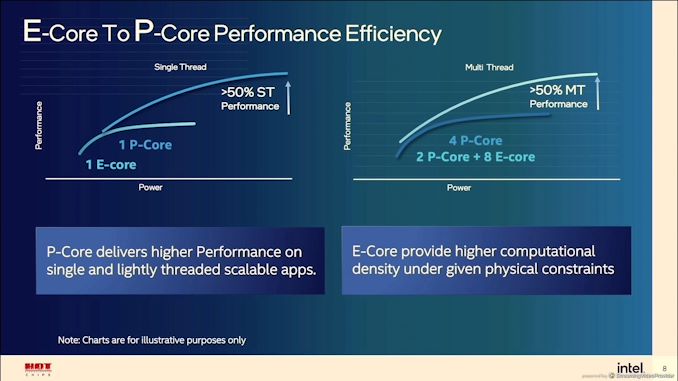

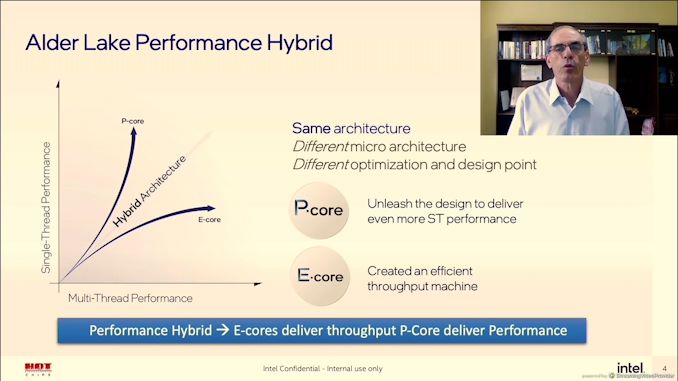

12:04 p.m. EDT – P-core is + 50% ST performance compared to E-core

12:04 p.m. EDT – E-core shared L2

12:03 p.m. EDT – P-Core and E-Core

12:03 p.m. EDT – This is what we saw in the Alder Lake portion of Architecture Day

12:02 p.m. EDT – Same arc, different uArch, different optimization point

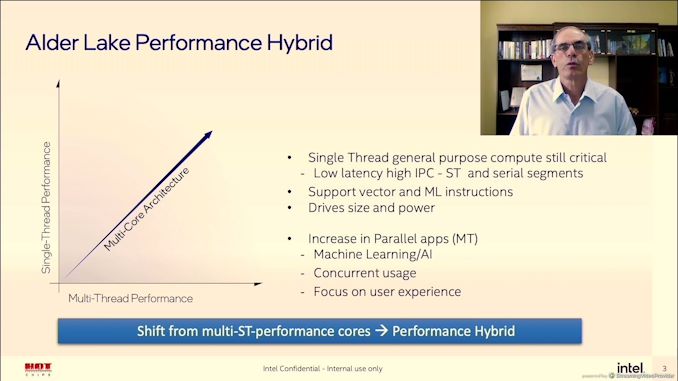

12:02 p.m. EDT – Moores law and Dennard scale

12:01 p.m. EDT – Multicore duplication

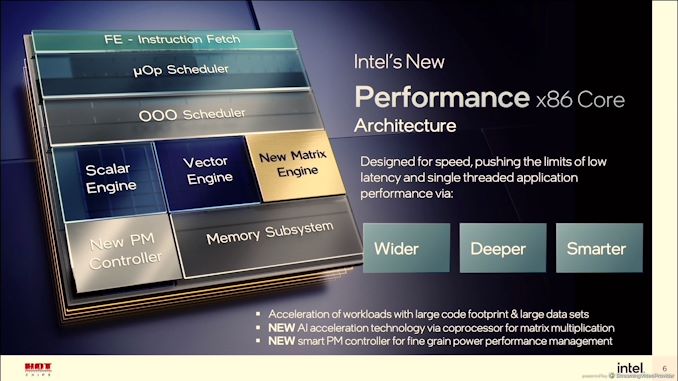

12:01 p.m. EDT – Work on smarter structures and new instructions for ML

12:01 p.m. EDT – Increased support for ML

12:00 p.m. EDT – Most applications are simple or slightly MT

12:00 p.m. EDT – The why and how of Alder Lake

11:59 a.m. EDT – Efi Rotem for Intel on Alder Lake

11:59 a.m. EDT – “State-of-the-art CPU”

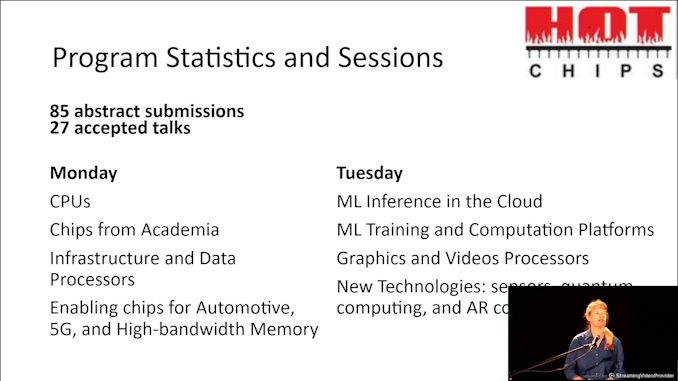

11:58 a.m. EDT – The first session is about processors, about to start

11:57 a.m. EDT – Posters for the conference as well

11:57 a.m. EDT – For participants

11:56 a.m. EDT – ‘Chips allowing chips’

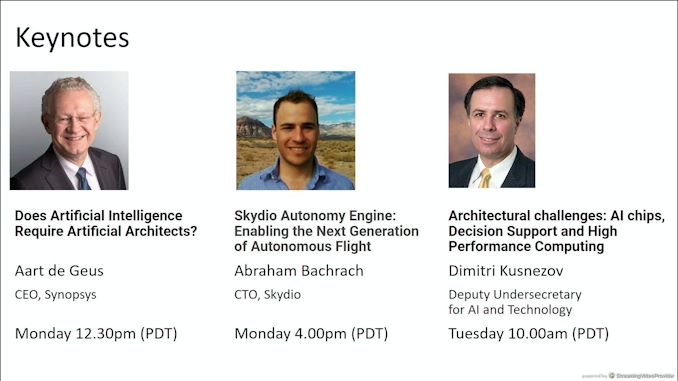

11:55 a.m. EDT – DoE on AI chips and challenges

11:55 a.m. EDT – Skydio in autonomous flight

11:55 a.m. EDT – Synopsys is on AI in EDA

11:54 a.m. EDT – Three speeches

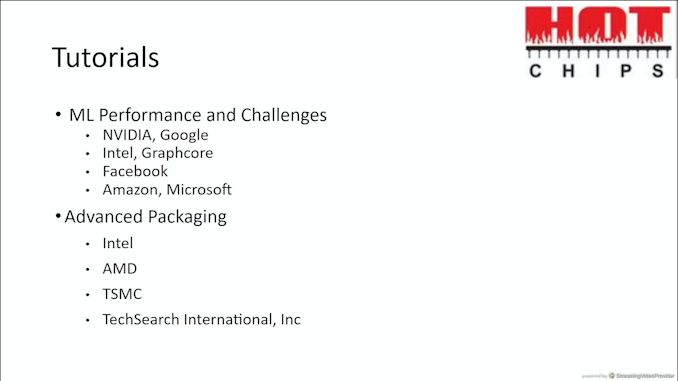

11:52 a.m. EDT – The tutorials were yesterday

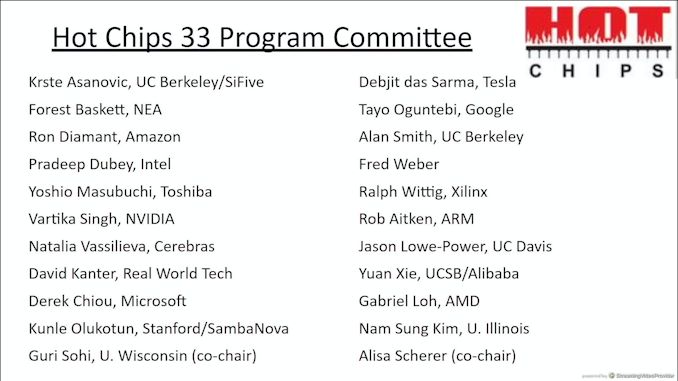

11:51 a.m. EDT – These people identify keynote speakers, solicit papers for conferences

11:51 a.m. EDT – Selection of the best speeches

11:51 a.m. EDT – Lots of committee members

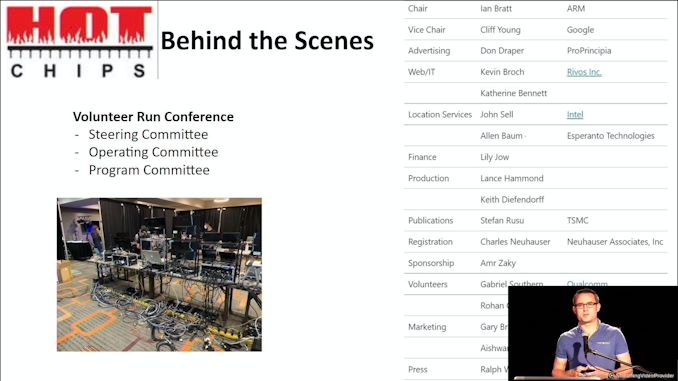

11:49 a.m. EDT – In the wings

11:49 a.m. EDT – There is a slack channel for all participants

11:48 a.m. EDT – Apparently some participants have issues with too many people from the same company on the same VPN

11:47 a.m. EDT – Here we are

11:45 a.m. EDT – It usually starts with 15 minutes of information before the show to start

11:45 a.m. EDT – The flow should start momentarily

11:40 a.m. EDT – Welcome to Hot Chips! This is the annual conference dedicated to the latest, best and upcoming big silicon that we are all passionate about. Stay tuned Monday and Tuesday for our regular AnandTech Live blogs. Today we start at 8:45 am PT, so set your watches and notifications to come back here! The first round of discussions is about processors: Intel Alder Lake, AMD Zen 3, IBM Z, and Intel Sapphire Rapids.

[ad_2]

Source link