[ad_1]

Intel has announced that the next family of Xeon processors is expected to be commercialized in the first half of next year. The new parts represent a substantial upgrade over current Xeon chips, with up to 48 cores and 12 channels of DDR4 memory per socket, supporting up to two sockets.

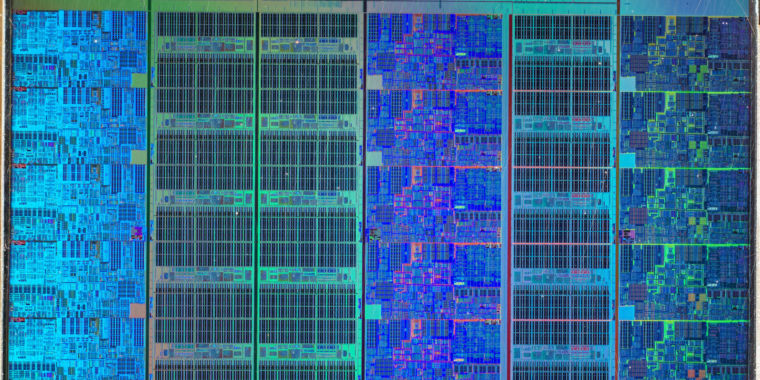

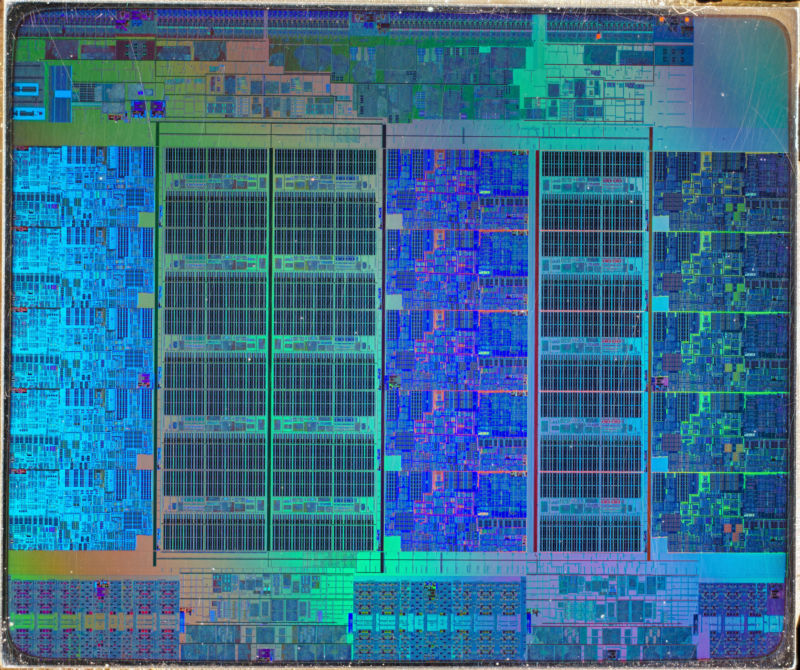

These processors will likely be Cascade Lake's upscale processors; Intel awards them the "Cascade Lake Advanced Performance" label, with a higher performance level than lower Xeon scalable processors. Current Xeon SP chips use a monolithic matrix, with a maximum of 28 cores and 56 nets. Cascade Lake AP will instead be a multi-chip processor with multiple arrays contained in a single package. AMD uses a similar approach for its comparable products; Epyc processors use four arrays in each enclosure, with each array having 8 cores.

The shift to a multiple-chip design is probably dictated by the need: as the matrices become larger and larger, it is increasingly likely that they will contain a defect. The use of several smaller matrices helps to avoid these defects. The Intel 10 nm manufacturing process is not yet powerful enough for mainstream production, so the new Xeons will continue to use a 14-nm process version of the company. Intel has not yet revealed the topology of each package. The exact distribution of these hearts and memory channels between chips is still unknown. The huge number of memory channels will require a huge power plug, which is currently considered a 5903-pin connector.

Intel, in particular, lists only a base account for these processors, instead of the usual base account / thread count combination. It's not clear if that means the new processors will not have any hyperthreading at all or if the company prefers to focus on physical cores and avoid some of the security issues that hyperthreading may present in some usage scenarios. Cascade Lake Silicon will contain hardware fixes for most variants of the Spectrum and Meltdown attacks.

Overall, the company reports a performance improvement of approximately 20% over current Xeon SPs and 240% over AMD's Epyc, with greater gains in workloads that consume significantly bandwidth. The new processors will include a number of new AVX512 instructions designed to improve the performance of functioning neural networks; Intel estimates that this will improve the performance of image matching algorithms up to 17 times faster than the current Xeon SP family. The small format used for performance comparisons indicates that simultaneous hyperthreading / multithreading is disabled on Xeon SP and Epyc systems.

At the other end of the performance spectrum, Intel said its latest generation of Xeon E-2100 processors is available today. These are single socket chips for small servers, offering up to 6 cores and 12 threads per chip. Functionally, they are Xeon versions of the main Core processors, with the difference that they support ECC memory and use a server variant of the chipset.

Source link